# **Controller for RF Power Amplifier Boost Converter**

### Features

- High Frequency Switching (up to 2 MHz)

- Optimized Output Drive Current (350 mA)

- Standby Mode

### Description

The Si9160 Controller for RF Power Amplifier Boost Converter is a fixed-frequency, pulse-width-modulated power conversion controller designed for use with the Si6801 application specific MOSFET. The Si9160 and the Si6801 are optimized for high efficiency switched-mode power conversion at 1 MHz and over. The device has an enable pin which can be used to put the converter in a low-current mode compatible with the standby mode of most cellular phones. A wide bandwidth feedback amplifier minimizes transient response time allowing the device to meet the instantaneous current demands of today's digital protocols. The input voltage range accommodates minimal size and cost battery pack configurations.

Frequency control in switching is important to noise management techniques in RF communications. The

- Wide Bandwidth Feedback Amplifier

- Single-Cell LiIon and Three-cell NiCd or NiMH Operation

Si9160 is easily synchronized for high efficiency power conversion at frequencies in excess of 1 MHz.

Optimizing the controller and the synchronous FETs results in the highest conversion efficiency over a wide load range at the switching frequencies of interest (1 MHz or greater). It also minimizes the overshoot and gate ringing associated with drive current and gate charge mismatches.

When disabled, the converter requires less than 330  $\mu$ A. This capability minimizes the impact of the converter on battery life when the phone is in the standby mode.

Finally, operating voltage is optimized for LiIon battery operation (2.7 V to 4.5 V) and can also be used with three-cell NiCd or NiMH (3 V to 3.6 V), as well as four-cell NiCd or NiMH (4 V to 4.8 V) battery packs.

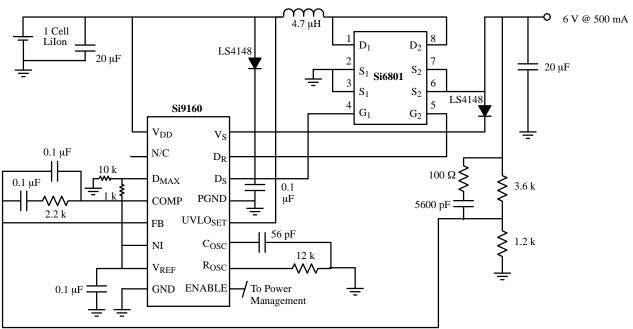

### **Application Circuit**

Updates to this data sheet may be obtained via facsimile by calling Siliconix FaxBack, 1-408-970-5600. Please request FaxBack document #1333.

### **Absolute Maximum Ratings**

Voltages Referenced to GND.

| •                                                                                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------|

| $V_{DD}, V_S \dots \dots 7 V$                                                                                                     |

| $P_{GND}  \dots  \pm  0.3 \; V$                                                                                                   |

| Linear Inputs $\dots \dots \dots$ |

| Logic Inputs                                                                                                                      |

| Peak Output Drive Current                                                                                                         |

| Storage Temperature                                                                                                               |

| Operating Junction Temperature $\hdots 150^\circ C$                                                                               |

|                                                                                                                                   |

| Power Dissipation (Package) <sup>a</sup> |         |

|------------------------------------------|---------|

| 16-Pin TSSOP (Q Suffix) <sup>a, b</sup>  | 925 mW  |

|                                          |         |

| Thermal Impedance $(\Theta_{JA})^a$      |         |

| 16-Pin TSSOP                             | 135°C/W |

Notes

a. Device mounted with all leads soldered or welded to PC board.

b. Derate 7.4 mW/°C above  $25^{\circ}$ C.

\* Exposure to Absolute Maximum rating conditions for extended periods may affect device reliability. Stresses above Absolute Maximum rating may cause permanent damage. Functional operation at conditions other than the operating conditions specified is not implied. Only one Absolute Maximum rating should be applied at any one time.

|                                        |                        | Test ConditionsUnless Otherwise Specifieda2.7 V $\leq V_{DD}$ , $V_S \leq 6.0$ V, GND = P <sub>GND</sub>                                                                                         |                    | <b>Limits</b><br>B Suffix -25 to 85°C |      |                  |      |  |

|----------------------------------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------------------------------------|------|------------------|------|--|

| Parameter                              | Symbol                 |                                                                                                                                                                                                  |                    | Min <sup>b</sup>                      | Тур  | Max <sup>b</sup> | Unit |  |

| Reference                              |                        |                                                                                                                                                                                                  |                    |                                       |      |                  |      |  |

| Orteret Valtage                        | V                      | $I_{REF} = -10 \ \mu A$                                                                                                                                                                          |                    | 1.455                                 |      | 1.545            | v    |  |

| Output Voltage                         | V <sub>REF</sub>       | $T_{\rm A} = 25^{\circ}{\rm C}$ 1.47                                                                                                                                                             |                    |                                       | 1.50 | 1.523            | 1 `  |  |

| Oscillator                             |                        |                                                                                                                                                                                                  |                    |                                       |      |                  |      |  |

| Maximum Frequency <sup>c</sup>         | f <sub>MAX</sub>       | $V_{DD} = 5 \text{ V}, C_{OSC} = 47 \text{ pF}, R_{OSC} = 5.0 \text{ k}\Omega$                                                                                                                   |                    | 2.0                                   |      |                  | MHz  |  |

| Oscillator Frequency Accuracy          |                        | $\label{eq:VDD} \begin{split} V_{DD} &= 2.7 \text{ V},  f_{OSC} = 1 \text{ MHz (nominal)} \\ C_{OSC} &= 100 \text{ pF},  R_{OSC} = 7.5  \text{k} \Omega,  T_A = 25 ^{\circ}\text{C} \end{split}$ |                    | -15                                   |      | 15               | %    |  |

| ROSC Peak Voltage                      | V <sub>ROSC</sub>      |                                                                                                                                                                                                  |                    |                                       | 1.0  |                  | V    |  |

| Voltage Stability <sup>c</sup>         | A C/C                  | $\Delta f/f = \frac{4 \text{ V} \leq \text{V}_{\text{DD}} \leq 6 \text{ V}, \text{ Ref to 5 V}, \text{T}_{\text{A}} = 25^{\circ}\text{C}}{\text{Referenced to } 25^{\circ}\text{C}}$             |                    | -8                                    |      | 8                | %    |  |

| Temperature Stability <sup>c</sup>     |                        |                                                                                                                                                                                                  |                    |                                       | ±5   |                  |      |  |

| Error Amplifier (C <sub>OSC</sub> = GN | ND, OSC DISAI          | BLED)                                                                                                                                                                                            |                    |                                       |      |                  |      |  |

| Input Bias Current                     | IB                     | $V_{NI} = V_{REF}, V_{FB} = 1.0 V$                                                                                                                                                               |                    | -1.0                                  |      | 1.0              | μΑ   |  |

| Open Loop Voltage Gain                 | A <sub>VOL</sub>       |                                                                                                                                                                                                  |                    | 47                                    | 55   |                  | dB   |  |

| Offset Voltage                         | V <sub>OS</sub>        | $V_{NI} = V_{REF}$                                                                                                                                                                               |                    | -15                                   | 0    | 15               | mV   |  |

| Unity Gain Bandwidth <sup>c</sup>      | BW                     |                                                                                                                                                                                                  |                    |                                       | 10   |                  | MHz  |  |

| Output Current                         | т                      | Source ( $V_{FB} = 1 V$                                                                                                                                                                          | , NI = $V_{REF}$ ) |                                       | -2.0 | -1.0             |      |  |

|                                        | I <sub>OUT</sub>       | Sink ( $V_{FB} = 2 V$ , $NI = V_{REF}$ )                                                                                                                                                         |                    | 0.4                                   | 0.8  |                  | mA   |  |

| Power Supply Rejection <sup>c</sup>    | PSRR                   | $4 V < V_{DD} < 6 V$                                                                                                                                                                             |                    |                                       | 60   |                  | dB   |  |

| UVLO <sub>SET</sub> Voltage Monitor    | - <b>-</b>             |                                                                                                                                                                                                  |                    | -                                     | -    | -                | -    |  |

| Under Voltage Lockout                  | V <sub>UVLOHL</sub>    | UVLO <sub>SET</sub> Hig                                                                                                                                                                          | h to Low           | 0.85                                  | 1.0  | 1.15             | v    |  |

|                                        | V <sub>UVLOLH</sub>    | UVLO <sub>SET</sub> Low                                                                                                                                                                          | v to High          |                                       | 1.2  |                  |      |  |

| Hysteresis                             | V <sub>HYS</sub>       | V <sub>UVLOLH</sub> – V <sub>UVLOHL</sub>                                                                                                                                                        |                    |                                       | 200  | 1                | mV   |  |

| UVLO Input Current                     | I <sub>UVLO(SET)</sub> | $V_{\rm UVLO} = 0$ to $V_{\rm DD}$                                                                                                                                                               |                    | -100                                  |      | 100              | nA   |  |

## Specifications

# Specifications

|                                       |                      | Test ConditionsUnless Otherwise Specified <sup>a</sup> 2.7 V $\leq$ V <sub>DD</sub> , V <sub>S</sub> $\leq$ 6.0 V, GND = P <sub>GND</sub> |                            | <b>Limits</b><br>B Suffix -25 to 85°C |      | 0 85°C                 |      |

|---------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|---------------------------------------|------|------------------------|------|

| Parameter                             | Symbol               |                                                                                                                                           |                            | Min <sup>b</sup>                      | Тур  | Max <sup>b</sup>       | Unit |

| Output Drive $(D_R \text{ and } D_S)$ |                      |                                                                                                                                           |                            |                                       |      |                        |      |

| Output High Voltage                   | V <sub>OH</sub>      | $\begin{array}{c} V_{DD} = 2.7 \ V \\ V_S = 5.3 \ V \end{array}$                                                                          | $I_{OUT} = -10 \text{ mA}$ | 5.15                                  | 5.2  |                        | v    |

| Output Low Voltage                    | V <sub>OL</sub>      |                                                                                                                                           | I <sub>OUT</sub> = 10 mA   |                                       | 0.06 | 0.15                   | 1 `  |

| Peak Source Output Current            | I <sub>SOURCE</sub>  | V <sub>DD</sub> = 2.7 V                                                                                                                   | $V_S = 0 V$                |                                       | -300 | -250                   |      |

| Peak Sink Output Current              | I <sub>SINK</sub>    |                                                                                                                                           | V <sub>S</sub> = 5.3 V     | 250                                   | 300  |                        | mA   |

| Break-Before-Make                     | t <sub>BBM</sub>     | $V_{DD} = 6.0 V$                                                                                                                          |                            |                                       | 40   |                        | ns   |

| Logic                                 |                      |                                                                                                                                           |                            |                                       |      |                        |      |

| ENABLE Delay to Output                | td <sub>EN</sub>     | ENABLE Rising to OUTPUT, $V_{DD} = 6.0 V$                                                                                                 |                            |                                       | 1.4  |                        | μs   |

| ENABLE Logic Low                      | V <sub>ENL</sub>     |                                                                                                                                           |                            |                                       |      | 0.2<br>V <sub>DD</sub> | N/   |

| ENABLE Logic High                     | V <sub>ENH</sub>     |                                                                                                                                           |                            | 0.8<br>V <sub>DD</sub>                |      |                        | v    |

| ENABLE Input Current                  | I <sub>EN</sub>      | $ENABLE = 0$ to $V_{DD}$                                                                                                                  |                            | -1.0                                  |      | 1.0                    | μΑ   |

| Duty Cycle                            |                      |                                                                                                                                           |                            |                                       |      |                        |      |

| Maximum Duty Cycle                    | CYCLE <sub>MAX</sub> | V <sub>DD</sub> = 6.0 V                                                                                                                   |                            |                                       | 80   | 95                     | %    |

| Supply                                |                      |                                                                                                                                           |                            | -                                     | -    | -                      |      |

|                                       |                      | f <sub>OSC</sub> = 1 MHz                                                                                                                  | V <sub>DD</sub> = 2.7 V    |                                       | 1.1  | 1.5                    | mA   |

| Supply Current—Normal Mode            | I <sub>DD</sub>      | $I_{DD} \qquad \qquad R_{OSC} = 7.5 \text{ k}\Omega \qquad \qquad V_{DD} = 4.5 \text{ V}$                                                 | V <sub>DD</sub> = 4.5 V    |                                       | 1.6  | 2.3                    |      |

| Supply Current—Standby Mode           | 1 1                  | ENABLE = Low                                                                                                                              |                            |                                       | 250  | 330                    | μΑ   |

Notes

a.  $C_{\text{STRAY}} < 5 \text{ pF on } C_{\text{OSC}}$ . After Start-Up,  $V_{\text{DD}}$  of  $\ge 3 \text{ V}$ . b. The algebraic convention whereby the most negative value is a minimum and the most positive a maximum, is used in this data sheet.

c. Guaranteed by design, not subject to production testing.

4

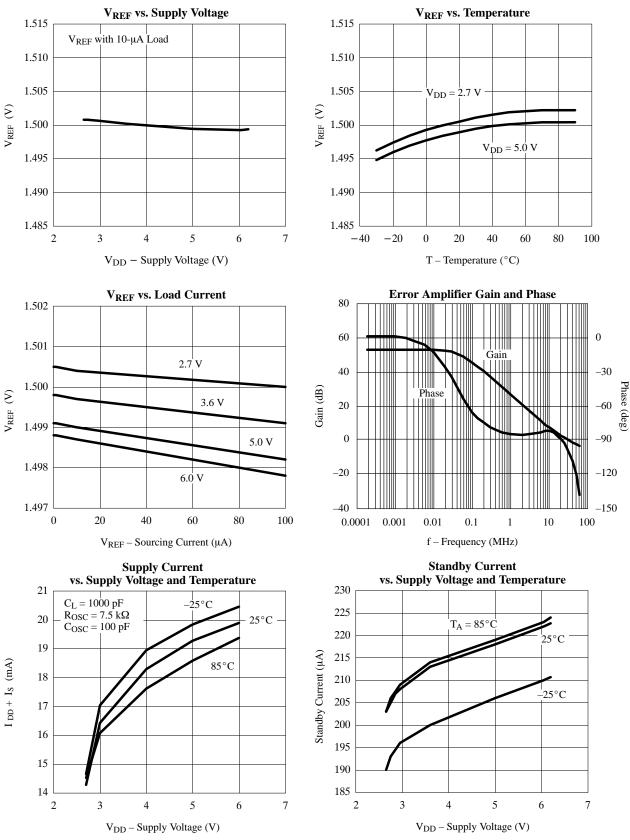

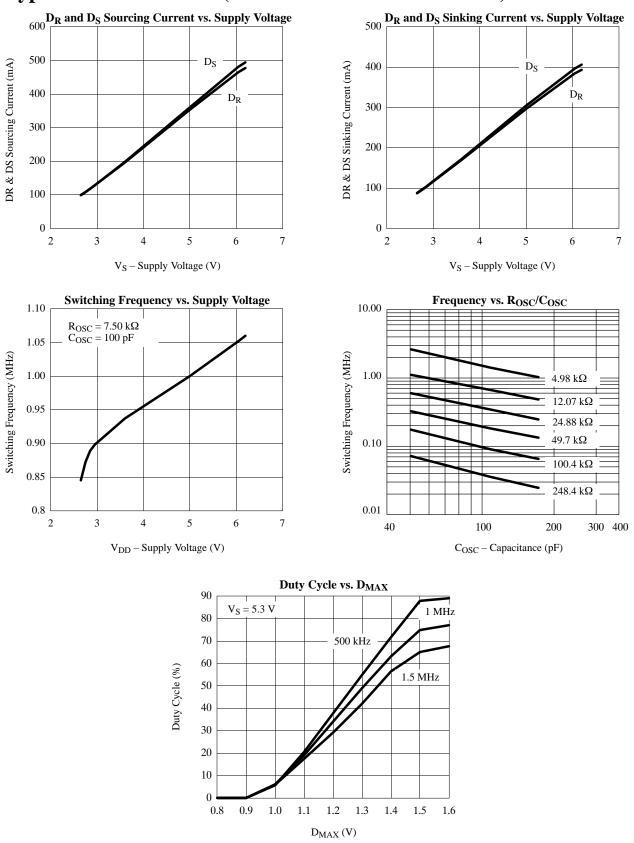

# Typical Characteristics (25°C Unless Otherwise Noted)

TEMIC Semiconductors

### **Typical Characteristics (25°C Unless Otherwise Noted)**

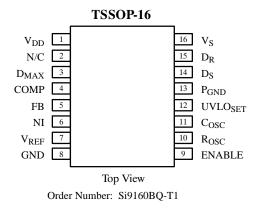

## **Pin Configurations**

### **Pin Description**

#### Pin 1: V<sub>DD</sub>

The positive power supply for all functional blocks except output driver. A bypass capacitor of  $0.1 \ \mu F$  (minimum) is recommended.

#### Pin 2: N/C

There is no internal connection to this pin.

#### Pin 3: D<sub>MAX</sub>

Used to set the maximum duty cycle.

#### Pin 4: COMP

This pin is the output of the error amplifier. A compensation network is connected from this pin to the FB pin to stabilize the system. This pin drives one input of the internal pulse width modulation comparator.

#### Pin 5: FB

The inverting input of the error amplifier. An external resistor divider is connected to this pin to set the regulated output voltage. The compensation network is also connected to this pin.

### Pin 6: NI

The non-inverting input of the error amplifier. In normal operation it is externally connected to  $V_{\mbox{\scriptsize REF}}$  or an external reference.

Pin 7: V<sub>REF</sub>

This pin supplies a 1.5-V reference.

#### Pin 8: GND (Ground)

#### Pin 9: ENABLE

A logic high on this pin allows normal operation. A logic low places the chip in the standby mode. In standby mode, normal operation is disabled, supply current is reduced, the oscillator stops, and  $D_S$  goes low while  $D_R$  goes high.

#### Pin 10: R<sub>OSC</sub>

A resistor connected from this pin to ground sets the oscillator's capacitor ( $C_{OSC}$ ) charge and discharge current. See the oscillator section of the description of operation.

### Pin 11: COSC

An external capacitor is connected to this pin to set the oscillator frequency.

$$f_{\rm OSC} \simeq \frac{0.75}{R_{\rm OSC} \, \times \, C_{\rm OSC}} \qquad (\text{at } V_{\rm DD} = 5.0 \ \text{V}) \label{eq:fosc}$$

### **Pin Description (Cont'd)**

#### Pin 12: UVLO<sub>SET</sub>

This pin will place the chip in the standby mode if the  $UVLO_{SET}$  voltage drops below 1.2 V. Once the  $UVLO_{SET}$  voltage exceeds 1.2 V, the chip operates normally. There is a built-in hysteresis of 200 mV.

#### Pin 13: P<sub>GND</sub>

The negative return for the V<sub>S</sub> supply.

#### **Pin 14: D**<sub>S</sub>

This CMOS push-pull output pin drives the external n-channel MOSFET. This pin will be low in the standby

mode. A break-before-make function between  $D_{\text{S}}$  and  $D_{\text{R}}$  is built-in.

#### Pin 15: D<sub>R</sub>

This CMOS push-pull output pin drives the external p-channel MOSFET. This pin will be high in the standby mode. A break-before-make function between the  $D_S$  and  $D_R$  is built-in.

#### **Pin 16: V**<sub>S</sub>

The positive terminal of the power supply which powers the CMOS output drivers. A bypass capacitor is required.

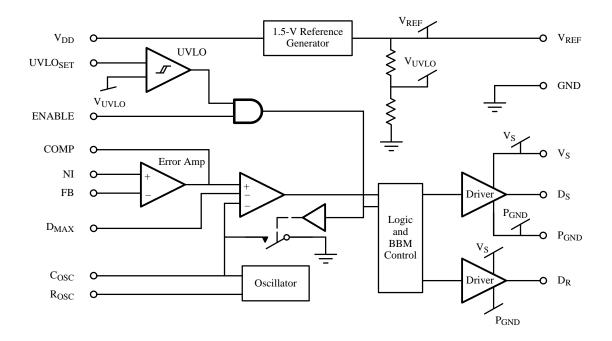

### **Functional Block Diagram**

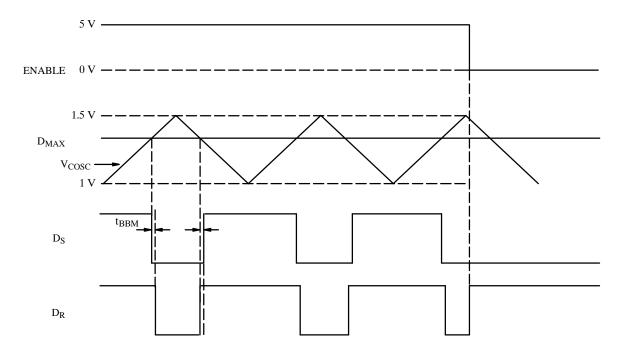

# **Timing Waveforms**

# **Operation of the Si9160 Boost Converter**

The Si9160 combined with optimized complementary MOSFETs provides the ideal solution to small, high efficiency, synchronous boost power conversion. Optimized for a 1-cell lithium ion, or 3-cell to 4-cell Nickel metal hydride battery, it is capable of switching at frequencies of up to 2 MHz. Combined with the Si6801, a complimentary high-frequency MOSFET, efficiencies of over 90% are easily achieved in a very small area.

#### **PWM Controller**

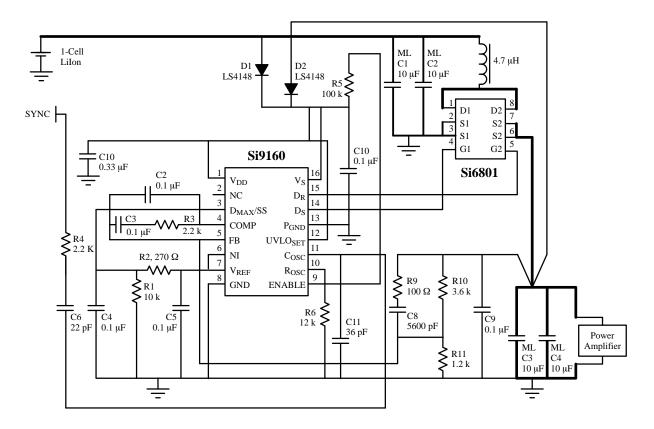

The Si9160 implements a synchronous voltage mode PWM control topology and is especially designed for battery power conversion. Voltage-mode control results in the most efficient power conversion solution. Figure 1 below illustrates a schematic for a synchronous boost converter with an input range of 2.7 V to 5 V which covers

the range of 1-cell LiIon and 3-cell or 4-cell NiMH/NiCd battery input respectively, and an output voltage of 6 V. Note the maximum input voltage is limited to the output voltage for a boost converter.

The switching frequency is determined by an external capacitor and resistor connected to  $C_{osc}$  and  $R_{osc}$  pins. The graph on page 5 in the Typical Characteristics section shows the typical  $C_{osc}$  and  $R_{osc}$  values for various switching frequency. Si9160 oscillator frequency can be easily synchronized to external frequency as long as external switching frequency. The synchronization circuit is a series resistor and capacitor fed into the  $C_{osc}$  pin of the Si9160. The synchronization pulse should be greater than 1.5 V in amplitude and a near square wave pulsed clock. Figure 1 shows typical values for the synchronization components.

Figure 1. Si9160 Boost Converter

#### Startup

Designed to operate with single cell Lithium Ion battery voltage, the Si9160 has an operating range of 2.7 V to 6.0 V. During start-up, the device requires 3.0 V to guarantee proper operation, although it will typically start up at less than 2.2 V. Once powered, Si9160 will continue to operate until the voltage at V<sub>DD</sub> is 2.7 V; at this point, the battery is basically dead. During start-up, power for the chip is provided by the battery through schottky diode D1 to V<sub>DD</sub> and V<sub>S</sub> pins. Once the converter is fully operating, supply power is provided by the converter output through diode D2, which overrides the D1 diode. This self perpetuating method of powering further improves the converter efficiency by utilizing higher gate drive to lower the on-resistance loss of the MOSFET.

Another benefit of powering from the output voltage is it provides minimum load on the converter. This prevents the converter from skipping frequency pulses typically referred to as Burst or Pulse-Skipping modes. Pulse skipping mode could be dangerous, especially if it generates noise in RF, IF, or signal processing frequency bands.

#### **Enable and Under Voltage Shutdown**

The Si9160 is designed with programmable under-voltage lockout and enable features. These features give designers flexibility to customize the converter design. The under-voltage lockout threshold is 1.2 V. With a simple resistor divider from  $V_{DD}$ , Si9160 can be programmed to turn-on at any  $V_{DD}$  voltage. The ENABLE pin, a TTL logic compatible input, allows remote shutdown as needed.

#### **Gate Drive and MOSFETs**

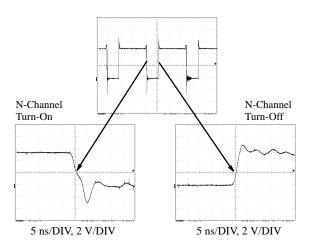

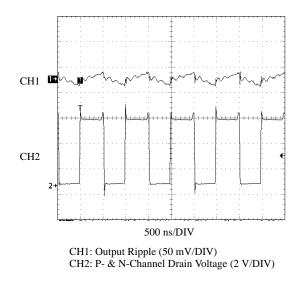

The gate drive section is designed to drive the high-side p-channel switch and low-side n-channel synchronous rectifier. The internal 40 ns break-before-make (BBM) timing prevents both MOSFETs from turning-on simultaneously. The BBM circuit monitors both drive voltages, once the gate-to-source voltage drops below 2.5 V, the other gate drive is delayed 40-ns before it is allowed to drive the external MOSFET (see Figure 2 for timing diagram). This smart gate drive control provides additional assurance that shoot-through current will not occur.

Figure 2. Gate Drive Timing Diagrams

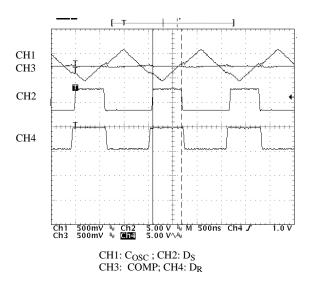

The MOSFET used is the Si6801, an n- and p-channel in a single package TSSOP-8. This package is called LITE FOOT<sup>®</sup>. The Si6801 is optimized to have very low gate charge and gate resistance. This results in a great reduction in gate switching power losses. The average time to switch on and off a MOSFET in a conventional structure is about 20 ns. The Si6801 will switch on and off in < 5 ns, see Figure 3.

#### Note the Speed

These MOSFETs have switching speeds of <5 ns. This high speed is due to the fast, high current output drive of the Si9160 and the optimized gate charge of the Si6801.

Figure 3. Gate Switching Times

#### **Stability Components**

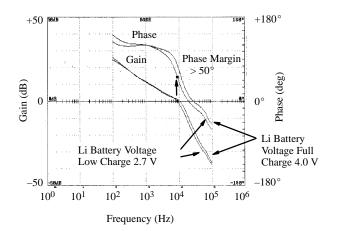

A voltage mode boost converter is normally stabilized with simple lag compensation due to the additional 90° phase lag introduced by the additional right hand plane zero, as well as having a duty factor dependent resonant frequency for the output filter. The stability components shown in Figure 1 have been chosen to ensure stability under all battery conditions while maintaining maximum transient response. To do this we have used a 2-pole-zero pair configuration (type 3 amplifier configuration). Figure 4 shows the bode plot for the above circuit, maintaining > 50° phase margin over the entire battery voltage range.

Figure 4. Stability, with 1-cell Li battery input, 5 V @ 600-mA output.

#### **Energy Storage Components**

The input and output ripple voltage is determined by the switching frequency, and the inductor and capacitor values. The higher the frequency, inductance, or capacitance values, the lower the ripple. The efficiency of the converter is also improved with higher inductance by reducing the conduction loss in the switch, synchronous rectifier, and the inductor itself. In the past, Tantalum was the preferred material for the input and output capacitors. Now, with 2-MHz switching frequencies, Tantalum capacitors are being replaced with smaller surface mount ceramic capacitors. Ceramic capacitors have almost no equivalent series resistance (ESR). Tantalum capacitors have at least  $0.1-\Omega$  ESR. By reducing ESR, converter efficiency is improved while decreasing the input and output ripple voltage. With ceramic capacitors, output ripple voltage is a function of capacitance only. The equation for determining output capacitance is stated below.

$$C = \frac{I_{OUT} \cdot (V_{OUT} - V_{IN})}{V_{OUT} \cdot \Delta V_{RIPPLE} \cdot f}$$

$$\begin{split} I_{OUT} &= \text{ output } dc \text{ load current} \\ V_{OUT} &= \text{ output voltage} \\ V_{IN} &= \text{ input voltage} \\ \Delta V_{RIPPLE} &= \text{ desired output ripple voltage} \\ f &= \text{ switching frequency} \end{split}$$

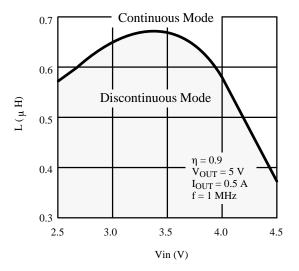

The inductance value for the converter is a function of the desired ripple voltage and efficiency as stated below. In order to keep the ripple small and improve efficiency, the inductance needs to be large enough to maintain continuous current mode. Continuous current mode has lower RMS current compared to discontinuous current mode since the peak current is lower. This lowers the conduction loss and improves efficiency. The equation that shows the critical inductance which separates continuous and discontinuous current mode at any given output current is stated below. This equation is also plotted in Figure 5 as a function of input voltage.

$$L = \frac{V_{IN}^{2} \cdot (V_{OUT} - V_{IN}) \cdot \eta}{2 \cdot V_{OUT}^{2} \cdot I_{OUT} \cdot f}$$

$\eta = efficiency$

Figure 5. Continuous and Discontinuous Inductance Curve

Designed with small surface mount inductors and capacitors, the Si9160 solution can fit easily within a small space such as a battery pack. Another distinct advantage of a smaller converter size is that it reduces the noise generating area by reducing the high current path; therefore radiated and conducted noise is less likely to couple into sensitive circuits.

# **Results Section**

The following section shows the actual results obtained with the circuit diagram shown in Figure 1.

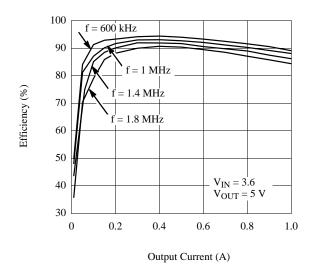

#### Efficiency

The graph below shows the efficiency of the above design at various constant switching frequencies. The frequencies were generated using a 3-V square wave of the desired frequency to the sync input to the circuit. The input voltage to the circuit is 3.6-V dc.

Figure 6. Efficiency of Si9160 and Si6801 Boost converter at various fixed frequencies

#### **Output Noise**

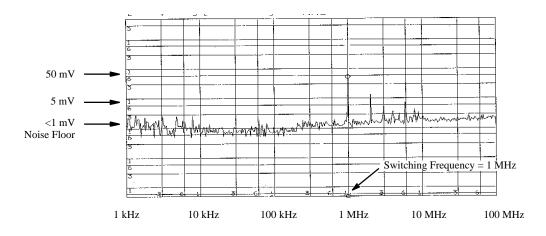

The noise generated by a dc-dc converter is always an issue within the mobile phone. The Si9160 offers two benefits.

- 1. The noise spectrum is a constant, i.e. no random noise or random harmonic generation.

- 2. The switching fundamental can be synchronized to a known frequency, e.g. 812.5 kHz which is  $^{1}/_{16}$ -th of the GSM/DCS system clock, 1.23 MHz which is the channel spacing frequency for CDMA, etc.

Figure 7. Output noise of the Si9160 demo board

Figures 7 through 9 show the output noise and output spectrum analysis.

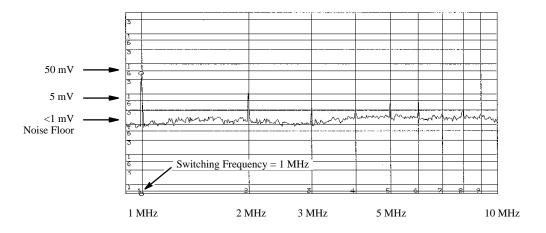

#### **Output Noise Spectrum**

Note there is no random noise, only switching frequency harmonics. This is very good news for the RF stages, where an unknown, or random noise spectrum will cause problems.

Figure 8. Spectrum response for the Si9160 demo board output voltage

Figure 9. Higher resolution of noise spectrum

#### Conclusion

Switching at high, known frequencies results in a smaller footprint while maintaining high efficiency. Efficiencies at high switching frequencies can be improved by using Si6801 optimized low gate charge and low gate resistance MOSFET. Additionally, synchronization to an external high frequency clock eliminates or greatly reduces any radio interference concerns and pushes harmonics out beyond signal processing frequencies.